新HPCの歩み(第125回)-1994年(g)-

|

IBM社はSP1に続くSP2を発表した。またメインフレームではS/390を発表した。Intel社とHewlett-Packard社は、IA-64 (Intel Architecture 64)の共同開発を発表した。Cray Research社は、J90などエントリレベルのスーパーコンピュータ商売に力を入れるようになって来た。Cray Computer社はCray-4を発表する。 |

アメリカ企業の動き

|

1) IBM社(SP2、PowerPC 603/604)

1994年4月5日、IBMは新しいPOWERparallel System (9076 SP2)を発表。4月5日Cornell Theory Centerが1号機を買うと発表された。ノードあたりPOWER2 CPUが1個であり、Thin 1, Thin 2 (66 MHz)、Wide 1 (66 MHz)、Wide 2 (77 MHz)の4種のノードがある。最大128ノードまでと発表されていたが、実際には512ノードが可能なようである。写真はIBM RS/6000 SP2 Type 7025(Computing Historyより)。

8月、日本IBMはSP2を民間セクターに販売を進めていくと発表。龍谷大学は10月SP2の設置を完了した。1996年11月のTop500に含まれる主要なSP2は以下の通り。

|

設置組織 |

機種 |

Rmax |

設置年 |

|

Cornell Theory Center |

SP2/512 |

88.4 |

1994 |

|

IBM社内 |

SP2/512 |

88.4 |

1995 |

|

Maui HPC Center |

SP2/384 |

66.3 |

1994 |

|

LLNL |

SP2/256 |

44.2 |

1996(2台) |

|

Pacific Northwest National Lab. |

SP2/208 |

36.45 |

1996 |

|

NASA Ames Research Center |

SP2/160 |

27.8 |

1994 |

|

KTH(スウェーデン) |

SP2/110 |

20.37 |

1996 |

|

MCI Worldcom(米) |

SP2/104 |

19.34 |

1994 |

これ以下は、なんと116件もある。日本に設置されたものとしては、以下の通り。

|

原子力発電技術機構 |

SP2/72 |

13.86 |

1995 |

|

東京都立大 |

SP2/60 |

11.75 |

1995 |

|

原子力研究所 |

SP2/50 |

9.90 |

1995 |

|

分子研 |

SP2/48 |

9.53 |

1995 |

|

東京理科大学 |

SP2/48 |

9.53 |

1996 |

|

統数研 |

SP2/48 |

9.53 |

1995 |

|

東北大学工学部 |

SP2/46 |

9.16 |

1996 |

|

中央大学理工学部 |

SP2/42 |

8.42 |

1996 |

|

国立がんセンター |

SP2/40 |

8.05 |

1994 |

|

キリンビール |

SP2/38 |

7.68 |

1996 |

|

東北大学 |

SP2/26 |

5.38 |

1996 |

|

国立環境研 |

SP2/24 |

4.99 |

1994 |

1994年12月には、第2世代のPowerPC 603とPowerPC 604が登場した。603は1チップ上に、32-bit PowerPCアーキテクチャを完全に実装したCPUで、ローエンド向けである。組み込みシステムなどに用いられた。604はサーバにも使える高性能のチップとして設計され、4命令同時実行可能なスーパースカラ・プロセッサであった。Power Macintosh 8500/9500やMacintoshクローンなどに採用された。また、ローエンドのRS/6000サーバやワークステーションにも使われた。1996年7月にはさらに高速化されたPowerPC 604eが導入される。

2) IBM社(メインフレーム)

1994年4月5日、IBM社はメインフレームS/390を発表した。ESA/390アーキテクチャを引き継ぎ、OSはVSE/ESA、VM/ESA、MVS/ESA、TPF(2000年からはLinuxも)などが動く。G1(1994年)からG6(1999年)まで6世代あるが、すべてCMOSを採用し、素子の性能の低下を並列処理で補強した。1997年のG4からはbipolarの性能を超える。(日本語WikipediaにはG1とG2はbipolarとあるが、英語版による)

3) Cray Research社(特許、J90、合理化)

Cray Research社と富士通は1994年7月、特許のクロスライセンス契約を結んだと発表した。両者は互いの特許を無償で利用することができる。Cray Research社によると、既にIBM社や日立とも同様な契約を結んでいるとのことである。

9月29日、Cray Research社、空冷の低価格ベクトルコンピュータJ90を発表した。これは買収したSupertek Computer社の遺産であるCMOSミニスーパーコンピュータCray Y-MP ELシリーズ(1993)を発展させたものである。クロックは10 ns(peak 200 MFlops/CPU)であるが、共有メモリで16並列の構成まで可能である。1995年3月には、メモリバンド幅を倍増し32並列まで構成できると発表。各プロセッサは、スカラ演算とベクトル演算を担当する2個のチップから構成されている。J98は8プロセッサ、J916は16プロセッサ、翌年発表されるJ932は32プロセッサである。この頃から、Cray Research社は、エントリレベルのスーパーコンピュータ商売に力を入れるようになっていた。

東北大学流体科学研究所は、1994年7月1日、Cray C90 (C916/161024)の導入を決定したと発表した。年末に設置され、1990年12月に設置したCray Y-MP/8を置き換える。1995年6月のTop500ではRmax=13.7 GFlops、Rpeak=15.24 GFlopsで70位にランクしている。

東京工業大学は、1989年に導入したETA-10の後継機の入札を行っていたが、8月、Cray Research社のC90(C916/12256)が日本電気のSX-3を押さえて落札したことが発表された。設置は1995年。1995年12月のTop500では、Rmax=10.27 GFlops、Rpeak=11.43 GFlopsで115位にランクしている。これまでのCrayの日本国内への販売実績は、産業界に31件に対し、公共機関には8件しかなく、今後公共セクターへのビジネスに期待していると表明した。

1994年9月9日のHPCwireにCray Research社の研究部門および製造部門があるChippewa Fallsのオペレーションが停止し、300人の正社員および82名の臨時社員をカットしたと報じられた。日本クレイ社広報は、これは計画的な合理化政策の一環であり、停止も一時的なものであり、財政面の悪化によるリストラではないと弁明した。Cray Research社がSGI社に買収されると発表されるのは1年半後の1996年2月26日であった。

Cray Research社の1972年からの初期メンバーであり、COOであったLester T. Davis (64)は1994年12月31日に引退した。Davisは、Cray-1, Cray X-MP, Cray Y-MPなどの設計の中心人物であり、1990年からは取締役を務めていた。

1993年、Rollwagenの後を継いでCEOとなったJohn F. Carlsonは、1994年に辞任した。1995年にJ. Phillips SamperがCEOに任命され、1996年にSGIに吸収後、辞任する。つまりCray Research社の最後のCEOとなった。

1994年、日本クレイの堀義和社長は、会長に昇進するとともに、米国Cray Research社の副社長にも任命された。

|

|

|

|

|

4) Cray Computer社(Cray-3/SSS、Cray-4)

Cray Computer社は資金繰りに苦しんでいた。2月27日に臨時株主総会を開き、新株の発行と外国への売却を承認した。この時点での債務超過は$20Mとのことである。

1994年8月に、NSAとCray-3/SSS (Super Scalable System)の共同開発契約を結んだ。ベクトルとSIMDのハブリッドマシンのようで、暗号解読用であろう。Thinking Machines社が1991年CM-5でSIMDを見捨ててしまったので、NSAはSIMDが欲しかったようである。でも他には売れそうもない。Seymourはこれでしばし息をつけるか?日本計算工学会に掲載された小林進の回顧録(現在はリンク切れ)によると、Cray-3/SSSは2 CPU + 256 MWのCray-3と512000個の1 bit processors (PIM – Processor-In-Memory)からなるとのことである。1995年3月の破産寸前に、デモまでは行ったようである。

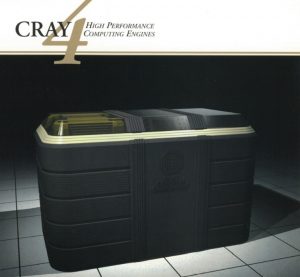

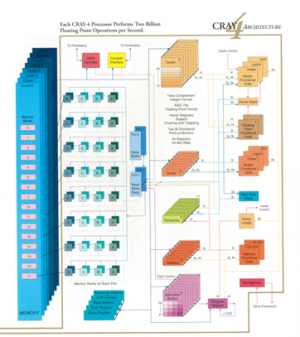

SC94のところで書いたように、Cray Computer社は11月10日、SC94を前にCray-4を発表した(写真)。Cray-4は基本的にCray-3を縮小して高速化したものである。テクノロジの比較表を示す。GaAsチップを高密度に集積し、クロック1 nsで最大32CPUまで構成でき、ピーク性能64 GFlopsとのことであった。新聞見開きの大きさの構成図を配っていて、もらってきたはずだが、現在行方不明。16ページのきれいなパンフレットはある(写真)。アーキテクチャのページも示す。メモリは8個のOctantに分かれ、各Octantは16バンク構成。CPUは1ボードから成り、その上には、8個のmemory ranks(メモリキューらしい)、64語のベクトルレジスタ8個、スカラレジスタ8個、ベクトル演算器、スカラ演算器等々が並んでいる。今後、Cray-5。Cray-6と続いていくと強気の発表であった。

|

Comparing the Technologies |

||

|

|

CRAY-3 |

CRAY-4 |

|

Logic Circuits |

GaAs SDFL 500 Gate-Equivalent 3.835×3.835 mm |

GaAs DCFL 5000 Gate-Equivalent 5.4×5.4 mm |

|

Memory Circuits |

Silicon CMOS SRAM 4 Meg×1 25 nsCycle Time 8 MWords per Module |

Silicon CMOS SRAM 4 Meg×1(4 Meg×4) 21 ns Cycle Time 16 MWords per Module |

|

Modules |

4.1×4.1×0.25 Inches Four Modules per CPU 69 Electrical Layers 22000 Z-axis Connections Twisted Pair Interconnect |

5.2×5.2×0.33 Inches One Module per CPU 90 Electrical Layers 36000 Z-axis Connections Micro-Caxial Interconnect |

|

Cooling |

Chilled Water/Fluorinert |

Also Air-Cooled Versions |

|

Cabinets |

System Tank and C-Pod |

System in One Cabinet |

|

Typical Footprint |

252 Square Feet |

215 Square Feet |

5) Intel社(Pentiumのバグ)

Intel社は1993年3月にPentiumを発表した、5月から出荷したが、1994年11月に、Pentiumの浮動小数除算命令にハードバグがあることが報告され、大騒ぎとなった。非常にまれなケースであるが、有効数字のかなり下の方に誤差が出得る。「インテル入ってる」でなく、「インテル狂ってる」と揶揄された。原因は除算用内部テーブルのバグらしい。これは非常に特殊な数値に対し起こるエラーであり、Intel社は「確率的に影響は少ない」と弁解したが、再現性のあるエラーなので、たまたまその数値の除算を実行した人にとっては100%の確率で起こる。Intel社の言い訳は厳しく批判された。筆者は「数値計算法」の講義をしていて、この話題に触れた。

6) Intel社・HP社(EPIC)

Intel社とHewlett-Packard社、IA-64 (Intel Architecture 64)の共同開発を発表した。これはEPIC (Explicitly Parallel Instruction Computer)アーキテクチャとも呼ばれ、HP社のVLIW技術を採用した。HP社は、自社のPA-RISCの後継と位置づけた。Intel 社は、x86(IA-32と呼ばれた)の後継を狙っていたようであるが、x86の64ビット化の普及により、当初の意図は実現しなかった。その後1999年にIA-64の詳細が発表され、これを実装したItaniumが初出荷されるのは2001年である。

7) Hewlett-Packard社(PA-7150、PA-7200、PA-7100LC)

HP社は1994年に、PA-RISC 1.1に基づくプロセッサPA-7150、PA-7200、PA-7100LCを発売した。PA-7100の改良版である。1995年第1四半期に発売されるHP9000サーバにはPA-7200が搭載される。PA-7100LCは業界初の低価格HPCチップであり、マルチメディア機能を組み込んである。これを搭載したシステムは1994年1月から販売されている。

8) Convex Computer社(Exemplar SPP、C4)

1991年末に、日本鋼管から約10名の開発担当者をDallasのConvex本社に派遣し超並列機の共同開発を進めていたが、Convex Computer社は、共有分散メモリ並列コンピュータExemplar SPPを1994年3月15日に発表した。8個のCPUがハイパーノードを構成し、4個のAgentには各2個のCPUが接続され、4個のメモリコントローラとともにクロスバでつながれている。ハイパーノード間は4本のinterconnect ringで通信を行う。これにより、システム全体にわたって共有メモリを実現している。

SPP 1000はPA-7100 (100 MHz)を、SPP 1200/1600はPA-7200 (120 MHz)を使用した。GaAsチップは富士通製で5種類(Agent, crossbar, memory controller, SCI interface, I/O)が使われている。CD (Compact Design)は2~16ノード、XA(eXtended Architecture)は8~128ノード。日本では共同開発者である日本鋼管が9月から発売した。

1994年6月頃、第4世代のベクトル計算機C4を出すという発表があった。1991年のところにも書いたが、1994年11月のTop500リストからC4の設置状況を示す。

|

組織 |

機種 |

Rmax |

ランク |

設置年 |

|

Ford Motor Company(米) |

C4/XA-4 |

2.531 |

223位 |

1994 |

|

CEDEX(スペイン) |

C4/XA-2 |

1.335 |

466位tie |

1994 |

|

国立台湾大学 |

C4/XA-2 |

1.335 |

1994 |

|

|

WPAFB(米) |

C4/XA-2 |

1.335 |

1994 |

他方、同社は1993年から四半期損失を出し続けており、会社の存続が危ぶまれた。1995年9月にHewlett-Packard社に吸収合併されることになる。

1995年11月のTop500から主要なSPPの設置機関を示す。このときはすでにHewlett-Packard社に吸収された後である。

|

設置機関 |

機種 |

Rmax |

設置年 |

|

Mainz大学(ドイツ) |

SPP-1200/XA-48 |

3.722 |

1995 |

|

CILEA(イタリア) |

SPP-1200/XA-32 |

3.722 |

1995 |

|

Convex(アメリカ) |

SPP-1200/XA-32 |

3.722 |

1995 |

|

Ford Motor(アメリカ) |

SPP-1200/XA-32 |

3.722 |

1995 |

|

政府機関(アメリカ) |

SPP-1200/XA-32 |

3.722 |

1995 |

|

Kentucky大学(アメリカ) |

SPP-1200/XA-32 |

3.722 |

1995 |

|

Convex(アメリカ) |

SPP-1000/XA-64 |

3.306 |

1994 |

|

HTC(ドイツ) |

SPP-1000/XA-64 |

3.306 |

1995 |

|

Josef Stefan Institute(スロベニア) |

SPP-1000/XA-64 |

3,306 |

1994 |

|

NCSA(アメリカ) |

SPP-1000/XA-64 |

3.306 |

1995 |

|

Erlangen大学(ドイツ) |

SPP-1000/XA-48 |

3.306 |

1994 |

|

JCCWC(アメリカ) |

SPP-1000/XA-32 |

3.306 |

1995 |

|

The Scripps Research Institute |

SPP-1000/XA-32 |

3,306 |

1884 |

|

東京大学(部局?) |

SPP-1000/XA-32 |

3.306 |

1994 |

|

US Naval R/D Center |

SPP-1000/XA-32 |

3.306 |

1995 |

|

Michigan大学 |

SPP-1000/XA-32 |

3.306 |

1994 |

|

Johannes Kepler大学(オーストリア) |

SPP-1000/XA-24 |

2.736 |

1995 |

SPP-1200でもSPP-1000でも32プロセッサ以上は同一のRmaxを出しているが、まじめに測定していないようである。

次回はアメリカ企業の続きと、ヨーロッパ企業の動きや企業の創業・終焉など。超並列スーパーコンピュータの雄と目されていたThinking Machines社やKendall Square Reserch社の経営破綻は大きな衝撃を巻き起こした。

|

|

|

2件のコメントがあります

S/390 は1990年の9月には発表されていました。上側のURLのとおりです。

(私もIBM Kingstonにいて、お祭り騒ぎをしていたのをみています)

最初に実際に顧客が買ったのはいつかはわかりませんが、4年間の間に

買い手がまったくつかなかったとは思われません。

二番目のURLのものは1994年の9月にアナウンスされた

S/390 CMOS 版です。

つまりS/390は1990年に発表されていた、その4年後にCMOS版が発表された。

それまでは従来どおり(メモリなどを除けば)主要な回路はECLであったと

思われます。

System/390 Announcement

https://www.ibm.com/ibm/history/exhibits/mainframe/mainframe_PR390.html

> The following is the text of an IBM U.S. Marketing & Services press

> release distributed on September 5, 1990.

S/390 Parallel Enterprise Server

https://www.ibm.com/ibm/history/exhibits/mainframe/mainframe_PP390G1.html

>The following is the edited text of an IBM product brochure published

>in September 1994.

著者です。今回の記事の最初にSP2の日本国内設置表があります。当初、1番目を「動燃」と書きましたが、「原子力発電技術機構」の間違いでしたので訂正しました。Top500でNuclear Power Engineeringとあったのを誤解していました。NUPECです。田村栄悦様からご指摘をいただきました。