AMD、3Dチップレットを披露、Zen 3 CPUでの垂直キャッシュをデモ

Tiffany Trader

AMDは、先週開催されたComputex 2021において、今年後半に発表予定の将来のハイパフォーマンス・コンピューティング製品に採用される新しい3Dチップレット・アーキテクチャを紹介した。AMDは、チップレットパッケージングとダイスタッキングを組み合わせた新技術を開発するために、半導体パートナーであるTSMCとここ数年にわたって緊密に協力してきたと述べている。

|

|

| 2021 Computexの基調講演で、新しい3D V-Cache技術を示すプロトタイプを掲げるLisa Su(出典:AMD/YouTube) | |

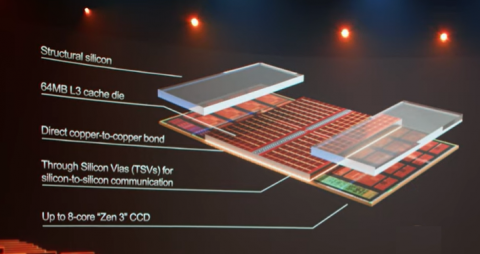

3Dチップレットの最初の用途は、3D垂直キャッシュ(3D V-Cache)である。この技術を実証するために、AMDはAMD Ryzen 5000シリーズプロセッサに3D垂直キャッシュをボンディングしてプロトタイプを作成した。AMDのシリコン貫通型ビア(TSV)を用いたハイブリッドボンドアプローチは、既存の垂直スタッキングソリューションと比較して、2Dチップレットの200倍以上、15倍以上の相互接続密度を実現しているという。AMDのCEOであるLisa Suは、「これにより、当社のIPをより効率的かつ高密度に統合することができます」と述べている。

AMD最速のゲーミングCPUであるRyzen 9 5900Xとの比較デモでは、3D V-Cacheを装着したプロトタイプのRyzen 5900Xが、Xbox Game Studiosのゲーム「Gears 5」で12%高いフレームレートを実現した。また、他の5つのゲームのベンチマークでは、3D V-Cacheテクノロジーを使用することで、パフォーマンスが平均で15%向上した。

ダイとダイの間のインターフェースは、銅と銅を直接接合しており、ハンダバンプではない。「このアプローチにより、熱伝導、トランジスタ密度、配線ピッチが改善され、マイクロバンプ方式の3Dアプローチに比べて、信号あたりのエネルギーが3分の1で済みます」とSuは言う。「これらのことから、この技術は世界で最も先進的で柔軟なアクティブオンアクティブシリコン積層技術であると言えます」とSuは述べている。

|

Ryzen 5000シリーズのプロトタイプ(下図)では、AMDは64MBの7nm SRAMを各コアコンプレックスの上に直接積層し、Zen 3コアが利用できるL3キャッシュを3倍に増やした。また、積層されたチップ間の信号や電力の受け渡しには、シリコン貫通型のビアを採用し、2テラバイト以上の帯域幅をサポートしているとSuは述べている。

|

|

| 試作品を手にするLisa Su、左のCCDには3D Vキャッシュが露出している(出典:AMD/YouTube) | |

量産チップでは、1つのコア複合ダイに96メガバイトのキャッシュを搭載し、1つのパッケージに収められた12または16のRyzenコアで合計192メガバイトのキャッシュを実現するとSuは述べている。

製造工程を説明すると、「3Dキャッシュダイを薄くし、構造用シリコンを追加して、複合チップの表面をシームレスにしました。完成した3D積層版のCPUは、実は現行のRyzen 5000プロセッサとまったく同じ外観です。」と述べている。

3Dチップレット技術は、同社の「最上位製品」を皮切りに、今年末までに生産する予定だとSuは述べている。

「今回のComputexにおける3Dチップレット技術の初適用は、ユーザ体験を大幅に向上させるためにハイパフォーマンス・コンピューティングの限界を押し広げ続けるという当社のコミットメントを示すものです」とSuは声明で述べている。

AMDは、この技術を初公開する具体的な製品については明らかにしていないが、コードネーム「Milan-X」と呼ばれる3Dチップレットを実装する新しいCPUの噂がある。

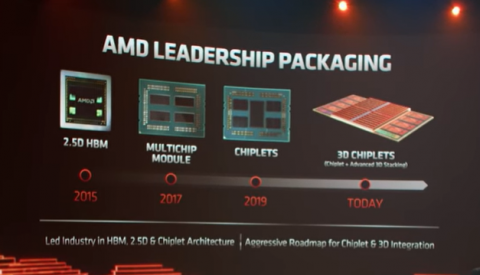

今回の発表は、2015年の2.5D HBMの導入に始まり、2017年に量産型マルチチップモジュール(MCM)パッケージをデビューさせ(Zen 1)、2019年にはI/Oをコンピュートコアとは別のプロセスで実現するチップレットを発表(Zen 2)するなど、AMDの革新的なパッケージングの進歩に基づいている。

|

主な競合メーカーであるインテルも、パッケージの進化に力を入れている。インテルは、2019年に56コアのCascade Lake-APチップを展開する際に、AMDを参考にして、2つのダイをマルチチップモジュールにまとめた。また、次期GPUライン「Xe」では、インテルのFoveros技術やEMIB技術を活用して、異なるメーカーが製造した異なる素子を1つのパッケージに統合できるタイルアプローチを導入している。

インテルのRaja Koduriは、3月に「先進的な高密度パッケージ(バンプピッチ55ミクロン以下)でパッケージングする必要のあるシリコンと、標準的なパッケージでパッケージングできるシリコンの “チップレット “を区別するために、”タイル “という名称に変更しました」と述べている。

インテルは、Computexの中で、第4世代のXeon Scalableプロセッサである10nmのSapphire Rapidsを2022年の前半に発売すると発表した。HPCwireに提供された声明の中で、インテルは次のように述べている。「Sapphire Rapids…は、2021年末頃に生産を開始し、2022年前半に立ち上がる予定です。」 Sapphire Rapidsは、Auroraスーパーコンピュータの一部であり、その最新版は当初2021年中にアルゴンヌに到着する予定であった。しかし、インテルの7nmノードの遅延により、このエクサスケールクラスのマシンは2022年に延期されている。これは、システムの性能のほとんどを提供するGPU「Ponte Vecchio」のスケジュールに影響を与えたためだ。

米国で計画されている他の2つのエクサスケールシステム(オークリッジのFrontierとリバモアのEl Capitan)には、AMDのテクノロジーが採用されている。次世代GPU「AMD Instinct」を搭載した「Frontier」(オークリッジ)は、AMDの第3世代「Epyc」カスタムプロセッサを採用する予定である。おそらく、噂されているMilan-X(または別のカスタムMilanチップ)が、AMDの新しい3D V-Cache技術とともにFrontierに搭載されるのではないだろうか。

少なくとも、私たちが話を聞いたあるHPCウォッチャーは、AMDの3Dチップレットのニュースに熱心に耳を傾けていた。

Intersect360 Research社のCEO兼創設者であるAddison Snellは、「AMDが計画している3Dチップレットの進化は、計算とメモリの両方で性能向上を追求し続けるHPCアプリケーションにとって非常に重要です。AMDのほぼ独占的なパフォーマンスへのこだわりは、競合他社との関係において特に興味深いものであり、インテルもSapphire Rapids CPUを今年中には一般販売できないと発表しています。」

編集部注:この記事では当初、インテルのSapphire Rapidsチップの発売が2021年後半から2022年前半に延期されたと報じていました。インテル社の報告によると、スケジュールに変更はないとのことです。記事はそれを反映して更新されました。

この件に関するインテルの公式声明全文。「我々はSapphire Rapidsのスケジュールを滑らせておらず、Sapphire Rapidsの時期にも変更はありません。2021年末頃に生産を開始し、2022年前半にランプする予定です。当社のデータセンター製品では、製品がお客様に出荷されてからしばらく経ってから、お客様の幅広い利用に合わせて正式な製品発表を行うのが一般的です。」