メニーコア “Piton”が最大200,000コアに向かっている

Tiffany Trader

Hot Chips会議は、IBM Power9プロセッサ(今後報告)や中国企業であるPhytium Technology社のカスタムのARMベースの64コアCPUを公表するステージとなったチップ打ち上げのための1週間であった。プリンストン大学から出た25コアのオープンソースのアカデミック;プロセッサもまたこのシリコンバレーのイベントでデビューしたのだ。

Piton (この名前はロッククライマーが使う金属スパイクを指している)は、現代の巨大な規模のデータセンターの需要を満足させるために、高速で高スケーラブルでエネルギー効率が高く設計されている。プリンストン大学の研究者らは8,000個のCPUを束ね合わせることで200,000コアのマシンを構築することが可能であると述べている。

「Pitonで、特にデータセンターやクラウド向けのチップを作るために、我々は座ってコンピュータ・アーキテクチャを再考したのです。」と公式声明の中で、プリンストンの電気工学および計算機科学科に関連する学科の准教授であるDavid Wentzlaffは述べている。「我々が作成したこのチップは、これまで大学で作られたチップの中で最大のもので、サーバがいかにはるかに効率的で安価に動作できるかを見せています。」

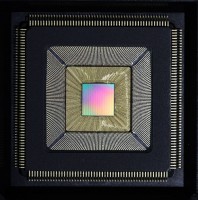

PitonはSPARC V9 64-bitのISAをベースとしており、Debian Linuxをサポートしている。2015年初頭に設計された後に、PitonはIBMの32nm SOIプロセスでテープアウトされた。6×6ミリメートルのダイは4億6千万個以上のトランジスタを搭載している。この研究者チームによれば、このシリコンは研究室内で試験されており、動作しているとのことだ。

|

|

Pitonのアーキテクチャは25枚のタイルを5×5の2次元メッシュ・トポロジーで接続している。各タイルは改変されたOpenSPARC T1コア(1GHz@.9 voltで動作)、L1.5キャッシュ、L2キャッシュ、浮動小数点ユニット(FPU)、キャッシュ・クロスバー(CCX)・アービター、および3つのNoCルーターで構成されている。オフチップのインターフェース(チップ・ブリッジ)はシステム当たり最大8,000チップ(200,000コア)までサポートするようにNoCとコヒーレンス・プロトコルを拡張しており、すべてのコアがメモリにアクセスできるようにしている。詳細についてはこの研究者のHot Chipsでの論文を参照。

Pitonは、キャッシュの領域と特定のコアを専用のアプリケーションにアサインすることができるハンドリングを行うユニークなキャッシュ・メモリを提供している。全体的に、彼らのデザイン上の決定がチップ当たり29パーセントの効率向上につながる、と研究者らは述べている。

|

|

このプリンストンの研究者らは2015年6月にPitonの設計をオープンソース化している。このチームによると、OpenPitonは初めてのオープンソースで、汎用、マルチスレッド化メニーコア・プロセッサである。この新興のオープン:ハードウェアのトレンドは、Facebookのオープン・コンピュート・プロジェクト(ラックレベルでの)や、先月RISC-V ISAベースのオープンソース・チップを立ち上げたファブレスのベンチャー企業であるSi-Fiveでもサポートされている。

「大規模な商業チップメーカーよりもはるかに少ないリソースというアカデミックな環境において、Pitonで達成したすべてのことに我々は非常に満足しています。」とWentzlaffは述べている。「また、世界にソフトウェアにおいては長い間ありふれたことでありましたが、ハードウェアではほとんど行われていなかったオープンソースとして我々のデザインを出すことについても満足しています。」

画像提供: プリンストン大学電気工学科David Wentzlaff