ムーアの法則 対 物理の法則

Tiffany Trader

おそらくHPCでないお友達や家族にムーアの法則の本質を10分以内の説明するすごいビデオをお探しなら、もう探す必要はない。直接的で簡単にフォローできる配信によって、ノッティンガム大学コンピュータ科学学部のDerek McAuley教授は今日のチップ設計者が物理学の法則に直面しているチップ設計と製造の要素を並べている。

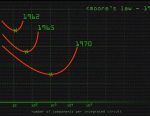

McAuley教授は、ムーアの法則を参照している – Gordon Mooreのある与えられた領域内でのトランジスタ数が2年毎に倍になるという観測だ。プロセッサの各世代で起きる「スイートスポット」として、毎回、チップの構成部品(例えば、トランジスタや配線)の特性サイズは縮小している。

教授は、同僚であるSophie WilsonやSteve FurberがARMプロセッサを設計していたAcorn Computingで働いていた、彼の経歴の初期の頃を振り返る。この時点で、彼らはトランジスタの特性サイズの3ミクロン技術に非常に興奮していた。今日の業界では28または22ナノメートルまで下がっている。

McAuley教授は、どうやってトランジスタがイオン添加された半導体素材(PまたはN素材)を使って作られるか、そしてムーアの法則を低速化させているか説明している。「各世代では、より良い理解ともっと複雑な光学系を必要としてきました。」と、McAuley教授は述べている。

「これらの特性サイズが小さくなると、トランジスタの領域に添加剤となる多くのイオンや原子を詰め込むことしかできなくなります。さらにもっともっと小さくなると、数はもっともっと少なくなりのです。ともて少ない数の原子しかないので、トランジスタの量子力学の動作と正しいことをする確率が減り始めるのです。」

McAuley教授は、ムーアの法則が尽きるのは、本質的にトランジスタが望ましくないことを頻繁にするようになった時であると述べながら話を続けた。エラー訂正はこの挙動をいくらか和らげるが、エラーが多すぎるようになったら終わりだ。

開発しなくてはならない多くの分野が他にあるが、McAuley教授はアーキテクチャの革新と3Dチップ設計における有望性を見ている。