中国のスタートアップBirenがBR100 GPUの詳細を発表

Oliver Peckham オリジナル記事

AMDとNvidia(そして間もなくIntel)の高性能GPUの縄張り争いの中で、新たに中国を拠点とするプレーヤーが台頭してきた。2019年に設立され、上海に本社を置くBiren Technologyである。Hot Chips 34では、Birenの共同創業者兼社長のリンジェイ・シュー氏とBiren CTOのマイク・ホン氏が(仮想)ステージに立ち、同社の初となる製品「Biren BR100汎用GPU(GPGPU)」を詳細に説明した。

「第一世代のコンピュート製品をBR100を発表できることを光栄に思います」とシューは語った。「BR100は、生産性の向上と総所有コストの削減を増強目標とし、データセンターにおけるAIトレーニングと推論の課題に取り組むことに専念しています。」

|

|

| 画像提供:ビレン |

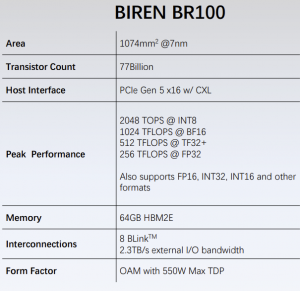

1074mm2の大きさに770億個のトランジスタ、デュアルダイのBiren BR100(ヘッダーの写真)は、TSMCの7nmプロセスで製造され、256 FP32テラフロップスが可能だ。ダイ間インターコネクトは896GB/sの帯域幅を実現する。BR100は最大64GBのHBM2Eメモリ(4スタック)を搭載し、8倍のBLink接続で最大2.3TB/sの外部I/O帯域を管理することが可能だ。これらにより、最大TDPは550W、目標クロック周波数は1GHzとなる。

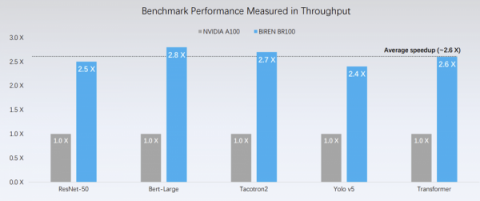

BR100がターゲットとするユースケースを考えれば、比較対象があるのは当然のことだ。NvidiaのA100 GPUは、アクセラレータの分野では事実上のリファレンスとなっている。もちろん、BR100のピークテラフロップスは、A100が19.5、BR100が256と、A100と比較して非常に有利である(「世界最速のGPUの1つ」とシュー氏は言う)。フロップス以外にも、ワークロードやベンチマークで有望な結果が得られているとシュー氏は言う。

「Nvidia A100と比較すると、現段階では、コンピュータビジョン、自然言語処理、会話型AIなど、さまざまな領域の幅広いベンチマークで平均2.6(×)のスピードアップが見られます」と述べた。「ハードウェアとソフトウェアの最適化を続けることで、今後数カ月はパフォーマンスが上がり続けるでしょう。」

|

| 画像提供:ビレン |

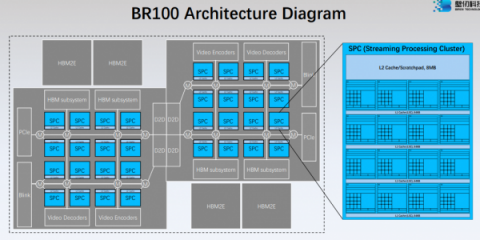

「BR100には2つの設計目標がありました」とホン氏は語る。「1つ目は、1ペタフロップスの馬力を達成すること。2つ目は、純粋なAIアクセラレータではなく、GPGPUであることです。」

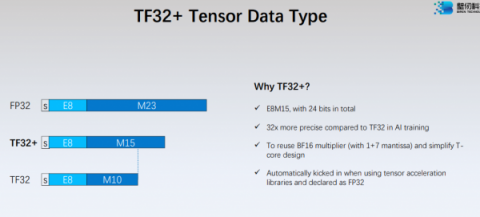

それを踏まえて、少しフロップに話を戻すと、BR100はFP32、BF16、FP16、INT32、INT16などのフォーマットをサポートしているが、さらに注目すべき点が2つある。1つは、BR100はFP64をサポートしていないこと(「ターゲットとする市場とユースケースにチップエリアを割くことにしました」、シュー氏はコメント)、2つはBR100がTP32+という新しい24ビットデータ型をサポートしていることである。また、BF16で1024テラフロップスの性能を持つBR100は、Birenの言う “1ペタフロップスの馬力 “に合致しているようだ。

|

BR100には、もう1種類、PCIeカード用に設計されたシングルダイの「BR104」も用意される予定だ。シュー氏によれば、Birenはメーカーと協力してリファレンスクラスターデザインを構築しているとのことだ。チップ自体はすでに実機でテストされている。さらに 「すでにMLPerfの最新ラウンドに応募しており、2〜3週間後には結果を見ることができるはずです」とシュー氏は語った。(BirenはMLCommonsのメンバー)

|

|

| 画像提供:Biren |

Biren Technologyは、Inspurと共同で8ウェイHearten OAMサーバを発表した。両社は、今年の第4四半期にこのハードウェアのサンプリングを開始する予定だ。

BIRENSUPAと呼ばれるBiren社独自のソフトウェアプラットフォームとプログラミングモデルを搭載したデバイスが出荷される予定だ。「(Nvidiaの)CUDAに慣れている開発者は、SUPA用のコードを簡単に書くことができます」とホン氏は述べた。サポートするAIフレームワークは、PyTorch、TensorFlow、PaddlePaddleなど。また、OpenCLのコンパイラも提供する。デュアルダイのBR100は、ソフトウェア層からは1つのGPUとして見える。

シリーズBの資金調達ラウンドの時点で、Birenは50億人民元(~7億3000万米ドル)以上の資金を調達している。

|

| BR100は、7nmチップレット設計とTSMCのCoWoSパッケージングを活用している。画像提供:Biren |