インテル、CPUとGPUの高性能チップのロードマップを統合する計画を再表明

Agam Shah オリジナル記事

インテルは、今後数年のうちに新しい製造プロセスやパッケージング技術に移行するため、高性能CPUとGPUのロードマップの統合に向けて順調に進んでいると改めて表明した。

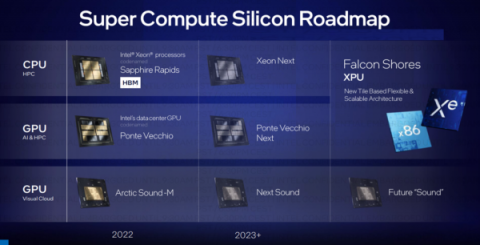

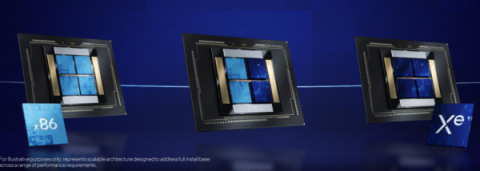

同社は、CPUとGPUのラインナップを、インテルがXPUと呼んでいるチップ(コードネーム「Falcon Shores」)に統合している。Falcon Shoresは、x86とXeのグラフィックスコアを1つのパッケージにまとめた「より大きなアーキテクチャ」の変更であると、ISC High Performanceスーパーコンピューティング会議に先立つ報道陣とのブリーフィングでインテルのスーパーコンピューティンググループ担当副社長兼ゼネラルマネージャのジェフ・マクベイ氏が述べた。

インテルは今年初め、Falcon Shoresが2024年後半に登場するロードマップを提示し、帯域幅、ワットあたりの性能、計算密度、メモリ容量に大幅な改善をもたらすと述べている。

Falcon Shoresのアーキテクチャは、チップレットアプローチを採用し、異なる製造プロセスで作られた複数のダイや異なるプロセッサモジュールを、1つのチップパッケージにぎっしりと詰め込むことができるようになるという。これにより、インテルはチップに搭載するCPU、GPU、I/O、メモリタイプ、電源管理などの回路の種類をより高度にカスタマイズすることができる。

|

Falcon Shoresは、「密接に結合したタイルを1つのパッケージで隣り合わせにすることで、あらゆるメリットを提供する」とマクベイ氏は述べ、「チップは、高度なパッケージング、IO機能、共有メモリ、これらのコンポーネント全体で単一のプログラミングモデルを持つことによって提供できるようになる」と付け加えた。

しかし、顧客が望むようなレベルのカスタマイズはまだできないとマクベイ氏は言う。

「XPUを自分で設計して、われわれがそれを生産するというようなことではありません。そのセットバージョンも用意します。しかし、市場が求めるワークロードに基づいて、設計プロセスのかなり後半で柔軟性を持たせることができます。過去5年間にAIが非常に普及したように、新しい技術があれば、新しいトレンドが到来したときに、より簡単に適応して設計内に配置できます」 とマクベイ氏は述べている。

Falcon Shoresは、共有メモリ環境で、より「CPUライク」なプログラミングモデルになるとマクベイ氏は言う。

「PCI Express上でディスクリートGPUを使用する場合のようなオフロード特性やレイテンシーに対処する必要はありません」 とマクベイ氏は述べている。

|

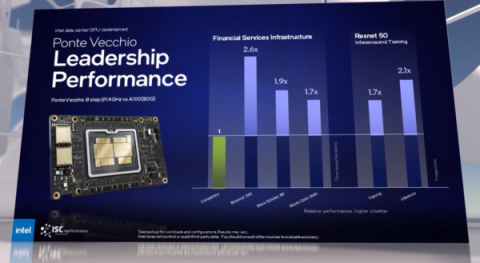

Falcon Shoresは、CPUとGPUチップのアップグレードをまだ2回残している。今年後半には、Sapphire RapidsとSapphire Rapids with HBMというコードネームのXeonチップを出荷する予定だ。また、今年の後半には、AIやハイパフォーマンスコンピューティング市場をターゲットとした、Ponte Vecchioというコードネームのスーパーコンピューティング用GPUを出荷する予定だ。

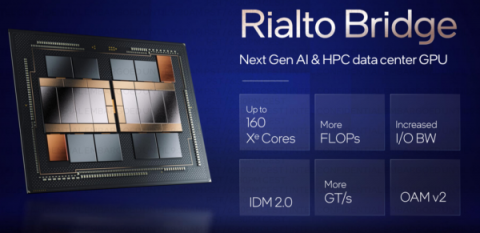

Ponte Vecchioの後には、Rialto Bridgeのコードネームで呼ばれる後継機が登場し、こちらはスロットアップグレードが可能になる。Rialto Bridgeは、アーキテクチャを段階的にアップグレードし、より多くのXeグラフィックスコアを搭載する予定だ。インテルは、特定のワークロードで30%の性能アップを目標にしているとマクベイ氏は語った。

|

マクベイ氏によれば、Falcon Shoresは、同社のチップ開発サイクル「tick tock」における「tick」アップグレードであり、新しい技術を搭載した全く新しいアーキテクチャを採用することを意味する。インテルは、Falcon Shoresのチップレット設計をサポートするために、先進的な製造プロセスとパッケージング技術を採用する予定である。

Falcon Shoresはまた、インテルがPonte Vecchioでエクサスケール性能を実現し、最終的にはゼタスケールコンピューティングに到達するための一歩を踏み出すことを意味している。同社は、帯域幅とエネルギー効率に対応するために、こうしたチップに光I/Oを統合するとしており、これはGPUの一部となる可能性もあるし、Falcon ShoreのXPUの一部となる可能性もあるという。

また、マクベイ氏は、メモリ階層や、Bonanza Mineというコードネームのビットコインチップで達成した性能とエネルギー効率など、その他のHPCに関する話題にも触れ、ハイパフォーマンスコンピューティング環境で必要となる低電圧クロッキングスキームの一例であるとしている。

|

| ISC 2022にてジェフ・マクベイ氏講演 |