IBM、3Dトランジスタで自己組織化を推進

Tiffany Trader

ムーアの法則の鍵は、各新しい世代に対して益々小さい半導体設計サイズを組み込む能力である。この「法則」に鎮座する指数関数的な進歩は過去10年間に鈍化してきたが、この結末はエンジニアが長く予測された終焉に先んじて対処することを強要している。

これらの回避策のひとつは、トランジスタを3次元方向に拡張することで、電力を抑えながらスイッチングを高速化できる効果がある。製造サイドにおいては、自己組織化と呼ばれる技術が、小さいが有用なパターンで自動的に自分自身を配置する分子を取得することで、より小さい回路素子を実現する方法として有望である。

最近のMIT Technology Reviewのゲスト寄稿者であるKatherine Bourzacの記事によると、IBMの研究者らがこれらのアプローチを組み合わせて、分子自己組織化による最初の3Dトランジスタを生成した。

Bourzacが説明するように、チップ製造とフォトリソグラフィの主要なイネーブラーの一つが、最速のマイクロチップに来た際に障害にぶつかった。一般的には14ナノメートルまで許容できると考られており、従来のフォトリソグラフィでは光の波長により制限されるポイントを超えると、あまりにも高価で複雑になると予測されている。

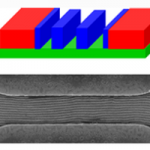

IBMの研究者らが採用したテクニックは、複雑な構造に自分自身を組み立てるようにされるブロック共重合体として知られている化合物の溶液を含んでいる。この方法により、リソグラフィで達成可能なものより高密度なパターンを生成可能となるのだ。このテクニックは従来の方法で提供するには最も難しい集積回路の最小要素に向けられている、例えばシリコントランジスタのチャネルや3Dトランジスタのフィンなどだ。回路の残りの部分については、標準的な製造技術でまだ十分であろう。

IBMの研究者グループはシリコンウェハーに深い平行なトレンチを作るのにフォトリソグラフィーを利用した。このトレンチはブロック共重合体の組み立てをガイドし、その後さらに小さい設計サイズにエッチングする化学プロセスのテンプレートとして機能する。最終結果は、リソグラフィーだけで可能なものよりも小さく高密度にパックされたトランジスタフィンを持った稼働装置となる。設計サイズはわずか29ナノメートルしか離れておらず、現在可能な80ナノメートルよりもかなり小さい、とBourzacは書いている。

潜在的なムーアの法則の延長として、チップ産業における自己組織化回路に関する話題はたくさんある。しかし、セミコンダクタ・リサーチ社のナノ製造のディレクターであるKowk Ng(元の記事でインタビューされた)によると、このプロセスは大量生産に適する前に制御される必要のある欠陥がまだあるとしている。