APS Marchミーティング、Google、インテルなど、量子進歩のポイントを紹介

John Russell

先日のAPS March Meeting 2022のQuantum in Industryセッションでは、Google、IBM、インテル、Quantinuum、Silicon Quantum Computing/サウス・ウェールズ大学(USW)が、量子コンピュータ実用化競争における進捗ポイントや現在進行中の課題について発表した。IBMは2023年を量子アドバンテージ達成の年と宣言しているが、他の参加者はQA達成時期について控えめな見解を示したものの、根本的な量子技術の課題解決に向けた進捗については前向きな見解を示した。

APS.org March Meetingは、量子コンピュータ関連研究の重要な場となっており、近年は多くの営利企業が複数のプレゼンテーションを行うようになっている。例えばGoogleは、今年のMMで少なくとも6件の発表を予定している。IBMは2019年にここでQVベンチマークを投じ、その後QVは他の数社に採用されている。3月のミーティングでの発表は、最近の仕事の結果を取り上げた粒度の高いものになる傾向がある。Quantum in Industryの招待講演は、通常、概要と深堀りの間にまたがり、それぞれの要素が含まれている。

Googleは、全体的な戦略とタイムラインを再確認した後、エラー訂正の研究とロードマップを深く掘り下げた。USW/Silicon Quantum Computing は,スケーリングと性能の利点をもたらすシリコンでの単一原子量子ビットの製造における進歩について議論した。IBM は、12 月に開催されたユーザーカンファレンスで議論した内容をほぼそのまま踏襲した。インテルは、量子ドット量子ビットの製造に CMOS 製造の専門知識を活用する能力を引き続き強調し、印象的な新しい低温ウェーハプローバに関する詳細も提供した。イオントラップを単独で発表した Quantinuum 社は、基本アーキテクチャ、イオン輸送、論理ゲート、量子ビットの初期化および検出における進歩について検討した。

Googleのスライドでは2029年、USW/SQCのスライドでは2033年、IBMのスライドでは2026年以降と、さまざまな予測が示された。しかし、いくつかのアプリケーションでは、量子的な利点をもたらすシステムがより早く登場する可能性があるという点で意見が一致しているようである。

今年のMarch Meetingは、対面式と仮想式のハイブリッドイベントである。インダストリーセッションは、シカゴ大学の量子研究者であるアンドリュー・クレランド氏が座長を務め、全発表の録画ビデオ(登録が必要な場合があります)が用意されている。ここでは、Googleのエラー訂正のアプローチに関するコメントの一部と、他の講演のハイライトを紹介する。(Quantinuumの講演は、私のZoomの品質が不安定だったため、この講演は含まれていない。)。量子の話題はいつもそうだが、プレゼンを直接見るのが一番だ。

エラー訂正とスケーリングに挑むGoogle

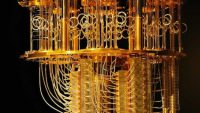

Googleはもちろん、超伝導量子ビットに賭けている。すべての量子ビット技術と同様に、さまざまなシステムノイズやランダムノイズは大きな問題であり、許容できないエラーレートを引き起こす。エラー訂正のためにいわゆるサーフェスコードを使うのも一つの方法であるが、そうすることは些細なことではなく、オーバーヘッドが必要である。Google Quantum AIのリサーチサイエンティストであるケヴィン・サツィンガー氏は、講演の中で表面符号(距離符号とも呼ばれることもある)を用いたGoogleの取り組みについて時間を割いて説明した。

「私たちが量子コンピュータで実行することを夢見るアルゴリズムでは、必要な結果を得るために、おそらく10-10から10-12のエラーレートが必要です。現代のハードウェアの典型的なエラーレートは10-3程度ですが、これは数桁の違いであり、エラーには大きな隔たりがあります。このギャップを埋めるのが量子エラー訂正です」とサツィンガー氏は言う。「このアイデアは、論理的な量子ビットを作成し、量子ビットの配列に論理的な情報を分散させるというもので、ここでは表面コードに注目しています。」

「つまり、dの2乗の物理量子ビットの配列になります、ここの青い量子ビットは、dがコード距離で、このように量子情報を分配することで、局所的なエラーに対して免疫ができるのです。しかし、その代償として、エラー訂正を行うために、余分なもの、オーバーヘッド、余分な演算が発生するのです。このオーバーヘッドがあるために、もしコンポーネントの性能が十分でなければ、余計なエラー訂正をすることで、益となるよりも害となる可能性があるのです」と彼は言った。

|

サツィンガー氏は、エラー訂正が「役に立つ」ようになる損益分岐点があるという。

「その(損益分岐点の)概念は、閾値と関連しています」と彼は言った。「論理ゲートあたりのエラーは、この比率に比例し、物理的な歩留まりあたりのエラーは、コード距離でこの乗に上げたエラー訂正の閾値で割られる、という(上の)スライドの下の方の式を考えてみましょう。この量、ラムダ上の1が小さな数であれば、コード距離のべき乗に上げることで、論理エラーを指数関数的に減らすことができるのです。それこそが、桁違いのキャズムを超えるために必要なことなのです。」

「しかし、このラムダを超えるものは、どのようなオーバーヘッドを必要とするのかが本当に重要なのです。例えば、ここの右辺(スライド参照)を10-12にしたい場合を考えてみましょう。その場合、ラムダ上の特定の1という値を見て、1つの論理的な量子ビットにいくつの物理的な量子ビットが必要かを表面コードで計算することができます。ラムダが1に等しい場合、損益分岐点にやっと到達したことになり、量は発散します。」

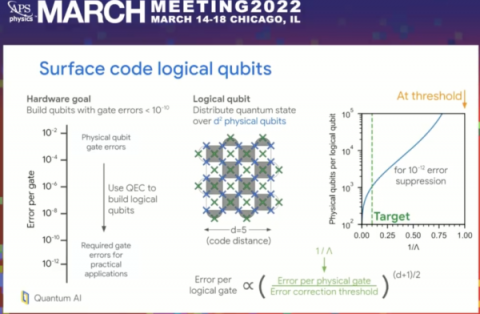

サツィンガー氏は、性能を向上させ、プロット(上のスライド)の左側に移動すると、必要なリソースは劇的に低下し、ラムダが10に等しくなると、1論理量子ビットあたり約1000物理量子ビットにまで下がると指摘した。「これが当面の目標です。このような背景から、今後予定されている2つのマイルストーンについて、もう少し詳しく説明します。まず1つ目は、論理量子ビットのプロトタイプを作ることです。これは、距離3表面コードと、より大きな距離5表面コードを実行し、その性能を比較できる装置を作るというものです。距離5表面コードの論理誤差が距離3表面コードより優れているという目標は、非常にチャレンジングなものです」と彼は言う。

|

量子誤り訂正に使用する距離符号については、これまでにも多くの研究がなされてきた。

「物理量子ビットのコヒーレンス時間と、距離3、論理量子ビットの有効な論理コヒーレンス時間の比較から、距離3コードに対する批判がしばしば見られるのですが、私はそれを指摘したいと思います。でも、距離3の論理量子ビットの寿命が物理量子ビットより短くても、私は一向に構わないんです。もし寿命が長ければ、それは素晴らしいことです。しかし、たとえば、10-12個の誤差を持つ大規模な誤差補正量子コンピュータがあったとして、そのデバイスで距離3のコードを作成しても、特定のパラメータによっては、それ自体が物理量子ビットよりも長い寿命を持つことはなく、あまり意味がありません」とサツィンガー教授は語る。

「これに対して、スケーリング動作は重要です。これに対して、スケーリング動作は非常に重要です。大きくして良くすることができなければ、企業全体がうまくいきません。だからこそ、私たちは、距離3と距離5のコードを見て、距離5が距離3よりも実際には優れていないように、より良いパフォーマンスを得るために、このスケーリング比較に焦点を当てているのですが、それには、これまで発表されたものよりも大幅に優れたパフォーマンスが必要になります」とサツィンガー氏は述べている。

シリコン量子コンピューティング/USW – シリコンにおける単一原子の量子ビット

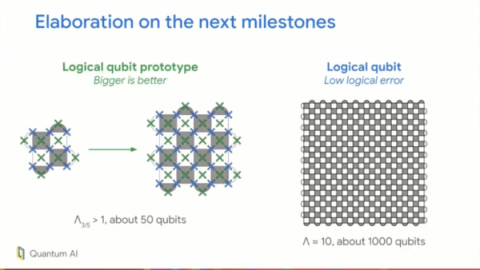

スタートアップ企業であるSilicon Quantum Computingの創設者兼ディレクターであり、量子物理学と凝縮系物質の著名な研究者であるミシェル・シモンズは、シリコン中に単一原子の量子ビット(リン)を作成する技術を理解し開発するというUSW/SQCの地道な作業について説明した。走査型トンネル顕微鏡(STM)を使って、彼女と彼女のチームは、これらの単一原子を精密に加工し、配列することができるようになりました。また、ナノワイヤー技術も開発した。

シモンズ教授は、2022年米国物理学会ベラー講演賞を受賞した。この講演会は、海外の著名な物理学者がAPSの会合で招待講演を行うための資金を提供するもので、シモンズ教授はこの講演会に参加した。彼女の講演、Manufacturing qubits in silicon with atomic precisionは、とても興味深いものであった。彼女と共同研究者は、電子の「位置」を画像化するまでに至り、それが曖昧でないことが判明したという。「多くの人は、ドナー原子の周りの電子雲を、ある種のファジーボールのようなものだと考えています。しかし実際には、STMの先端を使って中に入り、波動関数がどのように見えるかを直接画像化することができるのです。これは、結晶内の電子の位置がわかるので、非常に強力なツールです」と彼女は言う。

「私たちは、シリコン結晶表面にドーパントを決定論的に置く方法、ドーパントとリード状態を結びつける方法、ドーパントの位置を測定する方法、センサーを作り、そこに入ってスピン状態を測定する方法を見出したのです。シングルショットで読み出すことができ、これらのデバイスを通してスピン輸送を行い、その位置の計測を行い、独立して読み出すことができます。RFカップリングも可能です。これらのワイヤーは単層構造なので静電容量が非常に小さく、表面でのクロストークがほとんど発生しないことがわかりました。また、ワイヤが非常に小さいので、非常に忠実な読み出しが可能です。高速の2量子ビットゲートを実現し、読み出しのベンチマーク方法を見つけたので、キャビティ結合やコヒーレント制御を見ながら、このデバイスを使って最適化することができます」とシモンズ氏は語った。

|

IBM – 回路ニッティングによる性能向上

IBMは、量子研究者のハンヒー・パイク氏を中心に、ハード、ソフト、ツールの各分野で着実に進歩していることを紹介した。彼女はプレゼンテーションを担当し、近未来のアジェンダを簡単に紹介した。IBMは、量子コンピューティングの分野に早くから参入し、現在、さまざまなサイズの24の量子システムをオンラインにしている。そのロードマップでは、今年中に433量子ビットのシステムを、2023年には1000量子ビットを超えるシステムを提供する予定だ。

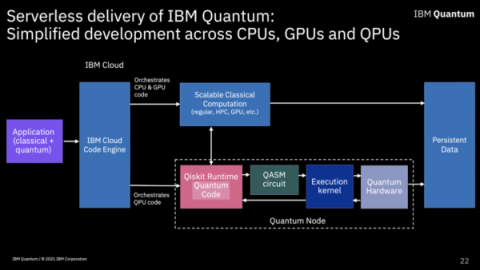

パイク氏は、低温での作業を可能にするために必要な材料研究の必要性を強調した。また、IBMのサーバーレスアーキテクチャなど、ユーザーフレンドリーな環境の構築に取り組んでいることも紹介された。

|

|

インテル – 極低温ウェーハプローブがスループットとフィードバックを高速化

インテルが量子コンピューティングを推進する中心的な理由は、CMOS製造に関する膨大な専門知識を活用することで、より速くスケーリングできるようになるという考え方だ。

インテル社の量子ハードウェアエンジニアであるオットー・ツァイツ氏は、このセッションで最も興味深いコメントの1つとして、「インテル社は毎年800兆個以上のトランジスタを出荷しているのはご存じでしょう」と述べた。「2025年には、地球上のトランジスタの数は人間の細胞の数を上回ると言われています。このように、膨大な数のデバイスが製造され、社会に送り出され、使われているのです。そして、インテル社のシリコンスピンクビットデバイスは、これらのトランジスタと非常によく似ていることがわかったのです。」

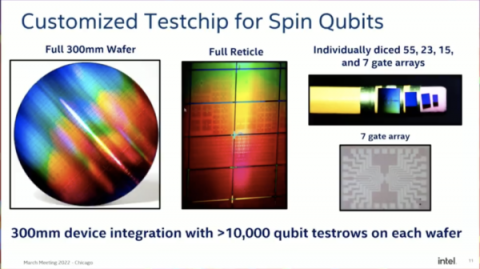

彼は、その量子ドット量子ビットの実際のファブプロセスについて、インテルが長い間、既存の14nmプロセスラインを使用すると言ってきた、ほとんど新しいことを言わなかった。インテルは、シリコン上のシリコン-ゲルマニウム技術でドット量子ビットを作成する。より興味深く、より新鮮なニュースは、インテルがウェハーの評価を進めていることである。

通常のトランジスタのプロセスを考えてみよう。インテルは、300mmウェーハで約1万個のデバイスを生産している。 「従来、当社のプロセスフローは、ウェーハが出てきたら、室温で特性評価するようなもので、これは、当社のアドバンストCMOSラインのHBMプロセスで行っていることと非常によく似ています。ここでは、数千個のデバイスを見ながら、ウェーハ全体で2時間程度でトランジスタのメトリックスを得ることができます」とZeitzは述べている。

「スピン量子ビットの領域に入ると、極低温でより多くの情報を得ることができるようになります。シリコン-ゲルマニウム-シリコンデバイスでは、埋もれたシリコンウェルの界面で接合を形成するため、室温ではその情報が得られません。量子ドット特性を正確に評価するためには、低温にする必要があります。量子ドットの特性評価を行うには、より低い温度で行う必要があります。ウェハー上の個々のデバイスをサイコロ状に切り、パッケージし、ロードして、約12時間で測定することができます。各デバイスの測定には約12時間かかります。 そして、ウェーハ全体から個別にサンプルを採取し、ウェーハ全体の性能を把握することができます。そして、最も有望なデバイスを希釈冷凍機に移し、量子ビットの形成と立方体の特性評価を行うことができます」とZeitzは述べている。

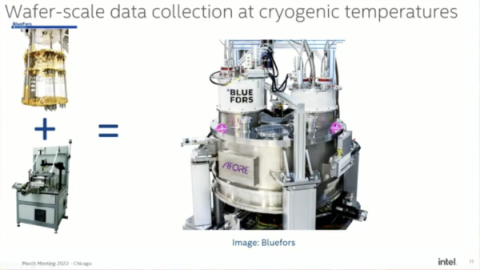

インテル社は、サプライヤであるBluefors社と協力してクライオウェハープローブを開発し、ザイツ氏はBluefors社から現在市販されていることを明らかにした。

|

|

「このツールは、パンデミックの初期に導入され、この間、データの収集を開始することができました。簡単に説明すると、このシステムの仕組みは、Bluefors社の2つの冷却システムとアフォー社の真空システム(真空チャンバー)を取り付け、このシステムの中にプローブカード、ウェハー、ウェハー上を移動するためのステージを入れて使用します。さらに、このシステムにはロードロックがあり、このロードロックによって、システムを大きく暖めることなくウェハーをシステムに移すことができます。研究開発工場からウェハーが出て、このツールにセットしてから、ケルビン以下の情報を収集し始め、量子ドットや低温物理学の関連情報を取得し始めるまで、約2時間かかります」 と述べている。

APS.orgへのリンク: https://www.aps.org