D-Wave、Advantage2プロトタイプを発表:ユーザによる検証とフィードバックを要請

John Russell オリジナル記事

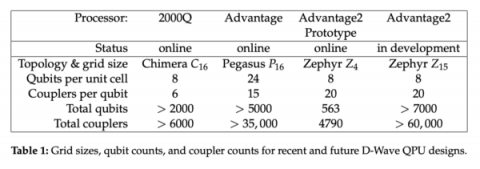

D-Wave Systemsは、2023年から24年にかけて発売予定の7000量子ビットの量子アニーリングコンピュータ「Advantage2」の500量子ビット以上のプロトタイプを公開している。このプロトタイプは、D-Waveの新しいZephyr量子ビットトポロジーに基づく、Advantage2の新しい20ウェイ接続を紹介するものである。また、現在進行中のプロセス改善も特徴としている。D-Waveによると、当初はプロトタイプの導入は予定していなかったが、Advantage2の開発が急速に進んだため、プロトタイプをユーザに公開し、検討してもらうことにしたという。

D-Waveでは、ユーザから得た知見を、半年前にClarityのロードマップの一部として発表したAdvantage2システムの最終版に反映させる予定だ。「Advantage2」は、同社にとって第6世代の量子システムということになる。さらに、新しい低ノイズ多層超伝導集積回路製造プロセスにより、量子ビットのコヒーレンスを高め、性能を向上させることができるとD-Waveは述べている。新しいプロセスで製造したチップの初期テストでは、量子ビットノイズが大幅に減少したことが報告されている。

「Advantage2プロトタイプは、Advantage2システムの完成に向けて、私たちが学んでいることを共有し、コミュニティからフィードバックを得るために設計されています。現在のAdvantage量子コンピュータは、ゼロから完全に再設計されたものです。Advantage2では、接続性とノイズの低減を実現することで、より高い性能を発揮できることを実証しています。Advantage2 のプロトタイプは、我々の興奮を共有し、お客様が量子技術を応用するための未来を垣間見ることができる機会です」とD-Wave 社の量子アニーリング製品担当ディレクターであるエミリー・ホスキンソン氏は、公式発表の中で述べています。

D-Wave社によると、このプロトタイプは、今後発売されるフルスケール製品のバージョンで、すべてのコア機能がテスト可能な状態になっているとのことだ。「初期のベンチマークでは、縮小版システムは、よりコンパクトな(回路)埋め込み、エネルギー規模の拡大によるエラー率の低下、解の質の向上と最適解を見つける確率の向上を実証しています。Advantage2のプロトタイプをLeap量子クラウドサービスで本日より利用できるようにすることで、開発者や研究者が探索し学習するための初期のスナップショットを提供します」と同社は報告している。

|

|

| ユーリッヒ・スーパーコンピューティングセンターにあるD-Wave社の量子アニーラー | |

D-Waveはもちろん、実用的な量子コンピューティングを実現するためのマラソンに早くから参加(1999年)している。量子アニーリングという量子コンピューティングの特殊版に着目し、最適化問題の解決に強みを発揮している。D-Wave社は、量子ビットに半導体ベースの超伝導技術を使用している。昨年10月、同社はシステム制御と製造の専門知識を活用して、ゲートベースの汎用量子コンピュータの開発にも着手し、多くの人を驚かせた。(HPCwireの報道、D-Wave Embraces Gate-Based Quantum Computing; Charts Forwardを参照)

ホスキンソン氏は、Advantage2プロトタイプ、システム開発に対するD-Wave社の進化したアプローチについてHPCwireに説明し、Advantage2に組み込まれている製造の進歩について少し触れた後、次のように述べた。しかし、当然のことながら、ゲートベースシステムの進展に関する詳細については、ほとんど触れなかった。

「ゲートベース開発について詳細を述べたり、具体的なスケジュールを示したいところですが、それはできません。ただ、言えることは、進捗がエキサイティングだということです。超電導回路アーキテクチャや製造プロセスの開発で培った豊富な経験を生かし、回路を拡張できることがわかり、勢いに乗っています。私たちは、スケーラブルでなければならないという観点から、この取り組みを始めています」とホスキンソン氏は語った。

「いろいろなことが起きています。最終的なゴールは、ゲートモデルと量子アニーリングの両方を含む完全なソリューションを顧客に提供することです。量子アニーリングは常にミックスの一部となるでしょう」と語った。

おそらくD-Waveは、10月に開催されるQubits 22カンファレンスで、ゲートベースの開発進捗に関する最新情報を提供する予定だ。D-Waveは、プロトタイプの発表と同時に、プロセスの進捗状況を説明するホワイトペーパー(Early Progress on Lower-Noise Fabrication Development for the Future, Full-Scale Advantage2 Quantum Computer)と、簡単な技術レポート(The D-Wave Advantage2 Prototype)を発表している。

ホスキンソン氏はHPCwireに対し、「プロトタイプの中心的なメッセージは、我々のロードマップが確実に進展しているということです。これは単なる研究プロジェクトではなく、単なる誇大広告でもありません。顧客は、自分自身でそれを確認することができるのです」とホスキンソン氏は語った。

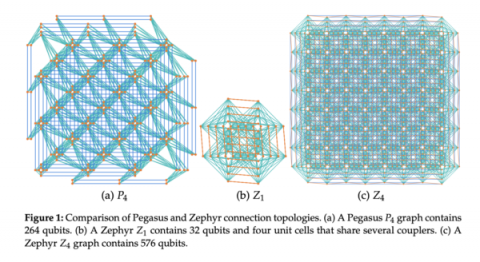

Advantage2 QPUとそのプロトタイプはともに、より高い量子ビットの接続性を特徴とする新しい量子ビット設計を採用しています。これは、Advantage QPUに搭載されているPegasusトポロジーをリプレースするZephyrと名付けた接続トポロジーによって実現されている、とD-Waveは報告している。「Zephyrでは、量子ビットの最大次数はd=20であり、各量子ビットは最大20個のカプラで隣接する量子ビットに接続されています。Pegasusの接続トポロジーはd=15です。次数が高いほど、量子チップへの入力はよりコンパクトになり、鎖も短くなります。埋め込み入力の鎖を短くすることで、より質の高い解を得ることができます。」

|

以下は、D-Wave社のテクニカルレポートからの抜粋である。

「プロトタイプは小型で、量子ビットの数は現世代のAdvantage QPUの約10分の1です。プロトタイプに搭載できるほど小さな入力では、性能を区別する余地があまりないため、実証的な比較は困難です。どちらの量子プロセッサも、テストでは小さな入力に対して最適または最適に近い解(最適から数パーセントポイント以内)を見つけるのにほとんど苦労していません。」

「しかし、両者とも解の質を向上させ、最適解が得られる確率を高める効果があることを実証しています。Advantage2プロトタイプは、4つのケーススタディにおいて、Advantage QPUを上回る性能を示しました。」

- よりコンパクトなエンベッディング。 プロトタイプに収まる程度の小さな入力では、Advantage2 QPU上のZephyr埋め込みは、Advantage QPU上のPegasus埋め込みよりも6%から21%鎖が短くなった。Advantage2プロトタイプとAdvantage(性能更新)QPUに埋め込まれた2つの入力クラスを用いた実証的な比較では、平均チェーン長で最大25%の改善が見られた。

- 埋め込み入力でのより良い解答。2つのカテゴリのSatisfiability入力を用いたテストでは、Advantage2プロトタイプソルバーは、最大82%のケースでAdvantageソルバーよりも高品質な解を発見した。

- ネイティブインプット に関するより良いソリューション。ネイティブ入力は、エネルギー規模の増加の寄与を分離するために使用されている(Zephyrによる埋め込み品質とは異なる)。4つの入力カテゴリのうち3つのカテゴリで,Advantage2プロトタイプソルバーは77%,87%,89%のケースでより良い解を求めました.(4つ目のカテゴリでは両ソルバーとも事実上同率で、常に最適解または二番手解を返した。このケースは、小さな入力に対する性能を区別することの難しさを示している)

- エネルギー規模の拡大によるエラー率の低減。逆有効温度の3つのコンポーネントレベルのテストが、量子ビット、カプラー、スモールチェーンに適用された。これらのテストでは、Advantage2プロトタイプにおいて、Advantage QPUと比較して、94%、103%、72%の改善が見られた。

|

物理学者であり、D-Wave社に11年間勤務しているホスキンソン氏は、D-Wave社の開発に対するアプローチが進化していることを指摘した。

「回路設計や製造、開発担当の異なるチーム間の緊密な連携など、当社の技術の重要な側面をすべて自社で管理するアプローチに、多大な投資を行ってきました。その結果、最近になってアーキテクチャーの開発を加速させることができました。これは、Advantageシステム(2000量子ビットシステム)から学んだことです。アーキテクチャと製造の同時開発では、問題が発生したときに、この2つの大きなカテゴリーを切り離すことが難しくなることがわかりました」とホスキンソン氏は言う。

「Advantage2では、この2つの側面を可能な限り分離することにしました。これにより、製造開発とは別にアーキテクチャーの開発を最適化することができ、その結果、当初は予定していなかったこの初期のプロトタイプをお客様に提供することができたのです。基本的に、この新しいアーキテクチャの設計は、最初の試みでうまくいきました。」

ホスキンソン氏は、ファブ・レシピの詳細については言及しなかった。D-Waveのチップは、現在SkyWaterがD-Waveと密接に連携して製造している。今回発表されたプロセスレポートも、製造の詳細は不明だが、性能指標は紹介されている。

ホスキンソン氏は、「全く新しい低ノイズ製造プロセスは、フルスケールの製品に使用される予定ですが、我々はかなりの進歩を遂げました。低周波のフラックスノイズは7倍、集積フラックスノイズは3倍、高周波のノイズは1桁減少していることが、今回発表するホワイトペーパーで明らかになりました。ノイズを減らすと量子ビットのコヒーレンス性能が向上することを示す多くの証拠があるため、これはエキサイティングなことです。つまり、プロトタイプで実証されたこれらのアーキテクチャーの改善だけでなく、フルスケールのシステムは、このプロセスで製造され、高いコヒーレンスを持ち、我々の量子アルゴリズムは長生きするのです。」

10月のミーティングでは、D-Waveの拡大する技術ロードマップについて、より詳細な報告を期待したい。

プロセスホワイトペーパーへのリンク、https://www.dwavesys.com/media/h0ylnsvg/2022-ac1-bb1-stack-comparison-v11.pdf

Advantage2プロトタイプのテクニカルレポートへのリンク、https://www.dwavesys.com/media/eixhdtpa/14-1063a-a_the_d-wave_advantage2_prototype-4.pdf