DDR6をサポートする最新のCXL仕様

Agam Shah オリジナル記事はこちら

数年後には、メモリ、ストレージ、アクセラレータが別々の筐体に移行するため、サーバーの見た目が変わるかもしれない。CXLと呼ばれるインターコネクトがそれを可能にしている。

今週、この技術のアップグレード仕様であるバージョン3.1が発表された。このアップデートは、より高速でセキュアなコンピューティング環境と、データセンターを巨大なサーバーに変えるより強固な技術基盤を提供する。

新仕様では、現在も開発中のDDR6メモリがサポートされる。DDRの標準化団体であるJEDECは、DDR6についてあまり詳しく語っていない。

現在、インテルとAMDのサーバーチップはDDR5をサポートしており、DDR6のチップセットサポートは案内されていない。大半のハードウェア・プロバイダとクラウド・プロバイダがCXLをサポートしている。

|

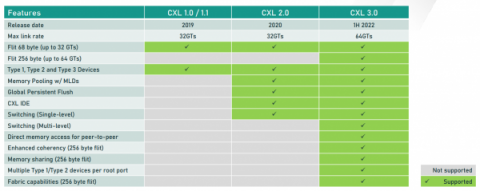

| CXLの機能進化 |

CXL 3.1は、1年以上前に導入されたCXL 3.0から段階的に改良されたものだ。CXLプロトコルは、システム内のチップ、メモリ、ストレージ間の通信リンクである。

CXL 3.0仕様はPCIe 6.0をベースとしており、データ転送速度は最大64ギガ転送/秒である。これは、PCIe 5.0をベースとする前身であるCXL 2.0よりも2倍高速で、サーバー・システムに採用されつつある。

CXLは、AIのような技術が普及するにつれて、チップセットの重要な一部となっている。機械学習アプリケーションは大量のメモリと帯域幅を必要とする。CXLは、サーバー間でストレージとメモリーの共有化を可能にする。

CXL 3.1プロトコルは、より多くのピアツーピア通信を開放し、メモリとストレージを個別のボックスに分解することができる。従来のネットワーキングやインターコネクト技術による分散化は10年前から議論されてきたが、CXLは幅広いコンピューティングリソースを利用できるようにするために必要な拡張性を提供する。

CXL 3.1仕様では、新しいタイプのメモリをサポートし、メモリやアクセラレータにより効率的にデータを再ルーティングできるようになった。

重要な進歩は、ファブリック上のメモリリソースを1つのグローバルアドレスにプールすることである。グローバル・インテグレーテッド・メモリと呼ばれるこの機能は、メモリと他のリソース間の高速接続を確立する上で重要である。

アクセラレータもメモリリソースと直接通信できるようになる。ポートベースルーティングの新機能は、メモリリソースへの高速アクセスを促進する。

CXL 3.1は、保護された環境でデータを実行するためのフックも提供する。この技術は機密コンピューティングをサポートするために導入されたもので、すでにインテルのSapphire RapidsではTDX命令で、AMDのチップではSNP-SEV機能として導入されている。

新しい仕様は、メモリ、プロセッサ、ストレージ間をデータが移動する際のセキュアな環境を拡張するセキュアなプロトコルを定義している。

このプロトコルは、コードや情報にアクセスするためにハードウェアの保管庫を開けるために、接続の認証が必要な環境を検出する。情報はプロセッサー、メモリー、ストレージのいずれかにある。インテル、マイクロソフト、その他の企業は、セキュアな環境でデータにアクセスしようとする接続を検証するために、さまざまなタイプの認証方法を持っている。