NTTと理研、量子コンピューティングの新しいロードストアアーキテクチャを発表

John Russell オリジナル記事「NTT, RIKEN Debut New Load-Store Architecture for Quantum Computing」

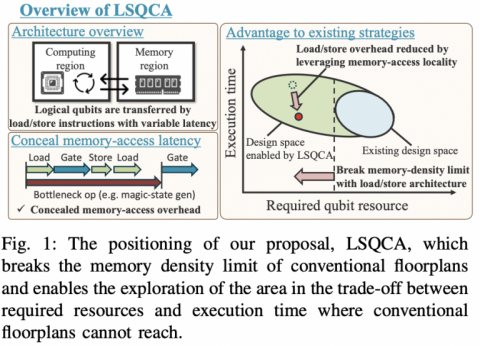

理化学研究所、東京大学、九州大学、そして日本の大手テクノロジー企業NTTの研究チームは、従来のコンピューティングアーキテクチャから着想を得て、新しいアーキテクチャ「Load/Store Quantum Computer Architecture (LSQCA)」をラスベガスで開催される第31回IEEE International Symposium on High-Performance Computer Architectureで発表する。

研究者らは、この新しい設計は、従来の量子回路ベースの設計におけるスケーリング、メモリ利用、移植性の問題を克服し、量子リソース要件を約40%削減できる実用的な耐故障性量子コンピューティングへの大きな一歩であると述べている。arXivには、プリプリント(LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing)が掲載されている。

この設計を新しいフロアプランやタスクフローと捉えてほしい。今日、量子エラー訂正(QEC)は量子コンピューティングが直面する最大の障害であり、既存のほとんどの量子コンピューティング・アーキテクチャは、エラー訂正された論理量子ビットを作成するために多数の冗長量子ビットを必要とするサーフェスコードの実装に依存している。NTT主導のグループは、量子チップ上のメモリの構成方法を変更することで、この問題に取り組んでいる。彼らのロードストアアプローチでは、従来のコンピューターが従来のチップ上のメモリとロジックを構成する方法とほぼ同様に、量子ビットを機能セクションに構成する。

以下に、問題と提案された解決策について述べた論文からの抜粋を引用する。

「現在のフォールトトレラント量子コンピュータ(FTQC)アーキテクチャでは、制限されたキュービット接続で信頼性の高い論理演算を可能にするために、複数のエンコーディング技術が利用されている。しかし、このような論理演算では、フォールトトレランスを確保するために追加のメモリオーバーヘッドが必要となる。実用的な量子コンピューティングの主な障害はキュービット数の制限であるため、計算能力を損なうことなくメモリオーバーヘッドを削減できるフロアプランを設計することが、私たちの主な課題である。FTQCアーキテクチャの探究に多大な努力が払われているにもかかわらず、現在の最先端のフロアプラン戦略でさえ、すべての論理キュービットへの単位時間でのランダムアクセスを保証するために、メモリの50%をこのオーバーヘッドに割り当て、データの保存には割り当てていない」と研究者は記している。

「私たちは、ほぼ100%のメモリ密度を実現できる新しいフロアプラン戦略、Load/Store Quantum Computer Architecture (LSQCA)に基づくFTQCアーキテクチャを提案する。このアーキテクチャのアイデアは、すべてのメモリ領域を、計算レジスタ(CR)と呼ばれる小さな計算領域と、スキャンアクセスメモリ(SAM)と呼ばれるスペース効率の良いメモリ領域に分離することである。これらの抽象的な構造に対して命令セットを定義し、ポイントSAMアーキテクチャとラインSAMアーキテクチャという具体的な設計を提供する。この設計により、他のボトルネックでレイテンシを隠蔽しながら、可変レイテンシのメモリアクセスを可能にすることで、メモリ密度を向上させることができる。」

古典的なチップとは異なり、量子チップ(大まかに言えば、制御回路を除く)は基本的にすべてメモリユニットであることを覚えておく価値がある。私たちはメモリレジスタを「キュービット」と呼び、通常はマイクロ波パルスを介してレジスタに論理実行を適用する。その意味で、この提案は量子チップのレイアウトの機能的再編成である。

「LSQCAは、量子プログラムにおけるアクセス局所性を利用することで平均レイテンシを改善できる、メモリ階層の一形態と考えることができる」と研究者は書いている。

|

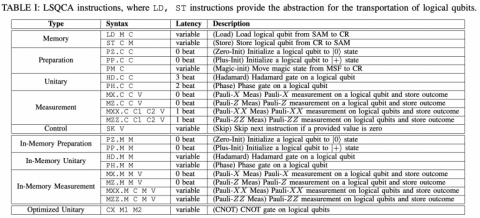

このアーキテクチャは、小さな演算領域と空間効率の良いメモリ領域を組み合わせるように設計されている。「このアーキテクチャでさまざまなアプリケーションプログラムを実行するために、従来のコンピュータにおけるレジスタとメモリの関係を参照しながら、2つの領域間のデータ移動を抽象化としてサポートする命令セットアーキテクチャを提案する。サーフェスコードに基づくFTQCについては、計算領域として計算レジスタ(CR)、メモリ空間としてスキャンアクセスメモリ(SAM)からなるLSQCAの実用的な設計を提案した。

このアーキテクチャでは、論理キュービットをSAMからCRにロードし、CRで論理演算を実行することができる。その後、ロードされたキュービットはSAMに再び格納される。SAMは、可変レイテンシのメモリアクセスを可能にしながら、平均レイテンシの増加を他のボトルネックに隠蔽することで抑制することで、ほぼ100%のメモリ密度を実現できる(図1)。CRとSAMの設計は、メモリオーバーヘッドとアクセスレイテンシのトレードオフを柔軟に調整することも可能にする。

|

チームが貢献と呼ぶもののリストは以下の通りである。

- LSQCAという新しいアーキテクチャを提案し、レジスタ・メモリデータ移動の概念をFTQCフロアプラン設計に導入する。

- LSQCAの命令セットアーキテクチャを提案し、CRとSAMを備えた設計を提供する。表面コードベースのFTQCと互換性のある2種類の設計、すなわち、メモリ効率、レイテンシ、およびアクセス局所性の利用という観点で異なる特性を示すポイントSAMアーキテクチャとラインSAMアーキテクチャを提供する。

- LSQCAの性能と実行時間オーバーヘッドは、現実的な量子プログラムとさまざまな構成を用いた数値シミュレーションにより評価される。その結果、LSQCAは実行時間のわずかな増加またはごくわずかな増加で、従来のフロアプランよりも高いメモリ密度を実現することが示された。

- リソースが制限されたシナリオでは、LSQCAは乗算器回路では実行時間が6%増加し、SELECT回路では実行時間が7%増加するものの、それぞれ従来のフロアプランと比較してメモリ密度を87%と92%に高めることができる。一方、従来のフロアプランでは、任意の論理量子ビットへの単位時間アクセスを保証するために、メモリ空間の50%が必要となる。

重要なのは、最近の研究は実際には実装されていないということだ。これは、量子プログラムに関する研究者の分析に基づいている。彼らは、「従来のフロアプランと比較して実行時間を5%増加させるだけで、約90%のメモリ密度を達成できることを示す特定のベンチマーク」を使用したと報告している。データがどのように移動するかの詳細は、論文に記載されている。

あるベテランのアナリストは興味をそそられながらも慎重な姿勢を示している。「これはある程度興味深いものの、革命的ではない。実際に構築して、規模の面で大きな改善を実証してもらいたい。」

設計は抽象的な形態として定義されているため、「この原理は至る所で適用でき、幅広い量子デバイス、キュービット接続構成、エラー訂正コードに適用できる」と研究者らは主張する。彼らは、フロアプランの最適化については他者による優れた研究が相当数あることを認めているが、彼らのアプローチは既存の密度限界を打破し、Tゲートを超えたアプリケーション特性を活かし、プログラムの移植性を提供する、と述べている。

結論として、研究者らは次のように記している。「このアーキテクチャは、アクセス頻度の低いキュービットの効率的な保存と、抽象化されたコンポーネント、SAMバンク、CR、MSFの仮想化されたアドレス指定を可能にする。我々は、サーフェスコードベースのFTQCの原始操作で実装可能な2つの設計、すなわちポイントSAMアーキテクチャとラインSAMアーキテクチャを提案した。実用的なインスタンスを用いた数値評価により、我々のアーキテクチャがメモリアクセスレイテンシのペナルティを隠蔽しながらメモリ密度を向上させることが示された。これは、我々のアーキテクチャがFTQCsによる量子優位性の実証を加速するのに有用であることを意味する。

今後の展開に注目

論文へのリンク:https://arxiv.org/abs/2412.20486