PhiベースのクラスタにおけるMPIベンチマーク

Tiffany Trader

Intel製のMeny Integrated Core (MIC) アーキテクチュアは、高並列アプリケーションがMPIに適合するように設計された。Intel Xeon Phiコプロセッサー上で動くアプリケーションは、GPGPUのためのCUDAプログラミングのアプローチに似た、オフロード・プログラミングを使う。つまり、CPUの上で動くアプリケーションが、ディレクティブ(ソースコードの指示行)によって、多くの計算をする部分のコードとデータを、ホスト・システムのメモリーからコプロセッサーへ送って実行するということである。しかしGPUとは異なり、Xeon Phiは、それぞれのコアがIPアドレスを持ち、ホストCPUの助け無しにMPIのノードとして動くこともできる。CPUから成るクラスター用に作られたプログラムを比較的容易にPhiへ移植できるので、いわゆる対称形のクラスターモデルは魅力的である。データをオフロードするようにコードを書き換えなくても、HPCアプリケーションの高速化が可能である。

ヘテロジニアスなノードから成る対称形のクラスターのセットアップにおいて、MPIプロセスは直接コプロセッサーにおいて開始される。複数のPhiコプロッセッサー間のピア・ツー・ピア通信は、OSによって仮想化され、

ヘテロジニアスなノードから成る対称形のクラスターのセットアップにおいて、MPIプロセスは直接コプロセッサーにおいて開始される。複数のPhiコプロッセッサー間のピア・ツー・ピア通信は、OSによって仮想化され、

ネットワーク機器を通して起きる。CPUのために開発されたMPIアプリケーションは、このように大きなコードの修正無しに動くかもしれない。しかし、ネットワーク・ハードウェアに特化していないために、通信の効率が落ちるかもしれない。

Colfax International の研究者 Vadim Karpusenko 氏と Andrey Vladimirov 氏は、PhiベースのクラスターをInfiniBandインターコネクトと適切なソフトウェアによって構築して、上記の欠点に対処した。彼らは最近の論文「 Configuration and Benchmarks of Peer-to-Peer MPI Communications Over Gigabit Ethernet and InfiniBand in a Cluster with Intel Xeon Phi Coprocessors」に研究の結果を掲載した。

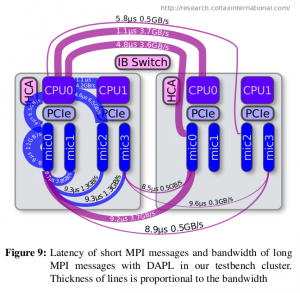

著者は、イーサーネット・ファブリック上のTCPプロトコルとインフィニバンド・ファブリック上のDAPLプロトコルを比較した。そして、よりよいインフィニバンドの構成がある場合とない場合について、MPIのレイテンシーとバンド幅を測定し、検討した。インフィニバンド・ベースのPhiクラスターにおけるMPIアプリケーションのチューニング方法も議論される。あるAsianオプション価格設定アプリケーションへの影響についてである。さらに著者は、HPCアプリケーションがPCIエクスプレス・バスを通す不均一なバンド幅を使う際の、多くの推奨を書いた。

実験には、 Colfax ProEdge SXP8600pワークステーションから成るクラスターを使い、それぞれのノードには4個の Xeon Phi 31S1Pコプロセッサーが搭載され、後述の2種類のネットワーク構成のうちの1つが選択された。

1. Intel Gigabit Ethernet adapters installed in the systems and connected to a D-Link Gigabit Ethernet switch.

2. Mellanox InfiniBand ConnectX-3 Single-Port VPI 4X QDR adapters connected to a 36-port Mellanox Infiniscale IV switch.

OSは、CentOS 6.5、カーネルは 2.6.32-431.e16.x86_64、MPSS 3.1.2、Intel MPI 4.1.1.036、OFED 1.5.4.1であった。著者は、性能測定のためにIntel MPIに含まれている、Intel MPIベンチマーク(IMB)を使った。MPIは、分散メモリーあるいは共有メモリー・システムにおける並列プログラミング・モデルで、通信に様々な種類のネットワーク設定とハードウェアを使えるが、この実験においては、Intel MPIライブラリーだけがクラスター内のIntel Xeon Phiコプロセッサーをサポートできる実装であった。

Xeon Phiコプロセッサーが、PCIエクスプレス・バスに接続されるエンド・ポイントデバイスであり、直接イーサーネットあるいはインフィニバンドの接続するポートを持たないことは、重要な注意点である。その代わりに、コプロセッサー内で動くLinux OSと、ホスト(CPU)の「Manycore Platform Software Stack (MPSS)」がコプロセッサーのネットワークを仮想化する。著者は、コプロセッサーの間でのピア・ツー・ピア通信の性質を詳述して、いくつかの可能性があるネットワーク構成を提案する。

論文の何ページかは、イーサーネットとインフィニバンドの通信について、著者がどのようにヘテロジニアスなノードから成るクラスターを構成し、MPIアプリケーションを動かしたかの説明に占められた。

著者が示したところによると、TCPプロトコル即ちイーサーネットは、オフロード・モデルのアプリケーションの要求を満たしているが、直接コプロセッサー上で起動されるヘテロジニアスなMPIアプリケーションについては、実際のハードウェアの限界よりも低速である。

さらに著者は、MPSSの上にインフィニバンド・コントローラーと関連するソフトウェアをインストールして、クラスター内のホストとコプロセッサーの間の通信を大きく改良した。ノード内のCPUとコプロセッサー、ノード間のコプロセッサー同士、ノード間のコプロセッサーとCPUの全ての通信についてである。

著者によると、「いくつかの場合についてバンド幅が下がることはありますが、Intel Xeon Phiコプロセッサーとインフィニバンドを組み合わせると、ギガ・イーサーと比べて、1桁から2桁通信が高速になります。」