AMD、新GPUチップレットのアプローチに関する特許を取得

George Leopold

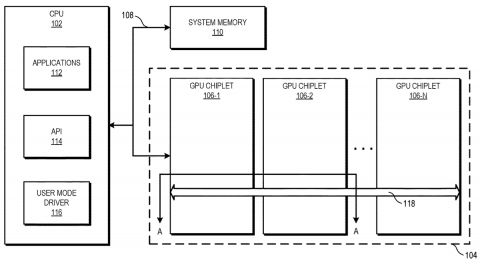

Advanced Micro Devices社は、プロセッサ・エレメント間の高帯域幅インターコネクトを組み込んだデバイスの米国特許出願を発表し、GPUチップレット競争を加速させている。

AMDとIntel Corp.はそれぞれ、チップレットアプローチを追求する意向を示しており、NvidiaのAmpereグラフィックスプロセッサのようなメガGPUからの移行を早める可能性が高いと業界関係者は指摘している。

AMDは、2020年12月31日に公開された特許通知の中で、クロスリンクと呼ばれる高速インターポーザ、つまり電気インターフェースを介してプロセッサ・エレメントをリンクするGPUチップレットアレイを開示している。この特許によると、AMDの設計では、2つのGPUチップレットを従来の通信バスを使ってCPUに接続する一方で、パッシブなクロスリンクが第2のGPUチップレットへのブリッジを提供するという。

特許によると、このリンクは、「チップレット間通信」専用のパッシブ・インターポーザー・ダイとして説明されている。また、このリンクは、より大きなSoC機能をより小さな処理タスクに分割する。

チップアナリストによると、この設計では「パッシブ・クロスリンクPHY」(もしくは物理層)も採用されているという。「ネットワークが複雑になるにつれ、リンクはアクティブでなければならなくなるでしょう」と、グラフィックス業界のアナリストであるJon Peddieは述べている。「AMDとIntelは、すでにそのような(通信)システムを構築していると想像できます」と述べている。

|

また、チップレット設計は、グラフィックス処理の並列性に対処する手段として、ますます注目されていう。これは、モノリシック・ダイ設計がますます複雑になり、製造コストが高くなっていることを意味している。そのため、プロセッサ・コンポーネントを分割するには、堅牢なコンポーネント・インターコネクトが必要となるのだ。

同社のチップレット設計では、メモリ間のクロスリンクを採用し、キャッシュレベルへの高速アクセスを可能にしている。「この低レイテンシ、チップレット間のキャッシュ・コヒーレンシーにより、ソフトウェア開発者の観点から、チップレットベースのシステムをモノリシックGPUとして動作させることが可能になります」とAMDは述べている。

チップレットベースの設計は、複数のコンポーネントを1つのパッケージにまとめていることから「チップレットベース」と呼ばれているが、汎用CPUが急激な性能要求に対応できないという問題に対処するために、ますます注目されるようになっている。低コストのチップレットは、ワークロードに特化したアクセラレータの必要性にも対応していると、推進派は指摘している。

AMD、Intel、Nvidia、およびその他のチップメーカーによる開発の加速は、Open Compute Projectのようなグループによる、個々のSoCアクセラレータ上で異なるベンダーのチップレットを混合して組み合わせることを可能にするオープンなインターフェイスとアーキテクチャを確立するための努力を反映している。

チップレット GPU の開発が進むにつれ、IC ベンダーは、現在の設計ツールを使用して個々のコンポーネントを単一のチップパッケージに高帯域幅の接続で統合することの難しさを指摘してきた。「チップレット技術をより使いやすくする必要があり、そのためには設計手法の面で我々ができることがあるのです」と、昨年の技術サミットでArm社の最高経営責任者であるSimon Segarsは述べている。

AMDは特許開示の中で、同社のパッシブ・ダイ・インターポーザーがモノリシックGPUの機能を「プログラマ・モデル/開発者の観点から、チップレットの実装を従来のモノリシックGPUのように見えるようにする方法で」展開すると述べている。

「これは全く理にかなっています」とPeddieは付け加え、Nvidia社のAmpereがモンスターGPUの最終ラインになると考えている。「AMDとIntelは、CPUとGPUのチップレット・アプローチに従うことを宣言し、示しています。」

AMDのチップレット・インターコネクト技術は、来年エネルギー省でオンライン化されるHPE Crayスーパーコンピュータに搭載される可能性があると、Moor Insights & StrategyのKarl Freundは指摘する。