インテル、UCIeがPCIeを上回るスピードと発表

Agam Shah オリジナル記事

インテルは、x86、Arm、RISC-Vアーキテクチャを1つのチップパッケージに共存させるという同社の長期計画の基盤となる、新しいインターコネクトの詳細を公開した。

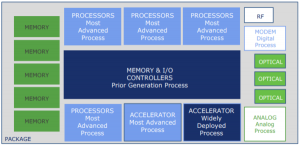

この半導体企業は、顧客がCPU、GPU、AIアクセラレータなどのコンピューティングブロックを1つのチップパッケージ内に詰め込むことができるよう、チップ設計にモジュラーアプローチを採用している。インテルは3月に他の9社と共同で、それらのコンピューティングブロックがチップ内で通信するための高帯域、低遅延のコネクタとしてUniversal Chiplet Interconnect Express規格を策定した。

|

|

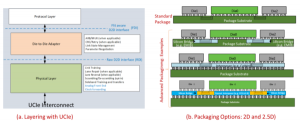

| SOCパッケージレベルの構築。複数のソースから異なるパッケージングオプションを持つダイを混在させる。出典 UCIeコンソーシアム | |

インテル ファウンドリー サービスのカスタマー ソリューション エンジニアリング担当副社長兼ゼネラル マネージャーのボブ・ブレナン氏は、テキサス州グレープヴァインで開催されたインテルの Vision カンファレンスの分科会で、「UCIe の最初の形態は、ピンあたり約 12 ギガビット/秒で、もう 1 つの形態は約 16 ギガビット/秒です」と述べている。

「消費電力に対する帯域幅を考えれば、(UCIeは)PCI Expressなどよりもはるかに優れています」と、ブレアナ氏は述べた。

UCIeの第一世代は、限られた数のパイプで同じ距離を移動する場合、PCI-Expressの約4倍の速度になるとブレナン氏は述べた。UCIeは、チャンネル間のパイプの数が多ければ、PCI Expressの10倍から20倍以上の速度になる可能性があるとブレナン氏は言う。

比較の対象は距離の関係だ。UCIeはチップレベルの基板上の非常に短い距離を想定して設計されているが、PCI Expressはマザーボードレベルで実装されており、データ転送の距離が長く、電気的要件も異なる、とブレナン氏は指摘する。

「UCIeは、チップのためのPCIeだと考えてください」とブレナン氏。

UCIeの設立メンバーには、AMD、Arm、Taiwan Semiconductor Manufacturing Co.、Microsoft、Qualcomm、Samsungが含まれている。Nvidiaは同月末、UCIe規格をサポートすると発表したが、UCIeのウェブサイトにはまだその名前は掲載されていない。

ハードウェアのほとんどを内部で設計しているAppleは、UCIeのメンバーでは無い。

「UCIeの第一弾として、パートナーや競合他社の幅広いコンソーシアムとともにこれを構築し、市場に投入することができました。UCIeの最初の形であり、これを市場に投入するために、幅広いパートナーや競合他社とともにこれを構築しました」(ブレナン氏)。ブレナン氏は、この仕様がいつ公開されるかのタイムラインは明らかにしなかった。

インテル社は、自社製x86コアをArmやRISC-Vアーキテクチャに基づくコンピューティングコアと一緒にパッケージできるように、チップをオープンにしている。例えば、XeonチップとRISC-VやArmのAIアクセラレータをパッケージで共存させることができる。ブレナン氏は、コアのパッケージを「チップレットシャーシ」と呼び、コンピューティングブロックをUCIeチャネルで接続している。

「チップレットシャーシのコンセプトは、顧客が作業するためのリファレンスデザインとなるシリコンシャーシを提供するというもので、概念的には我々がボード設計をするのと同じようなものです。その代わり、これはチップデザインで す」と、ブレナン氏は述べた。

|

|

| 出典 UCIeコンソーシアム | |

UCIeは、インテルのEMIB(Embedded Multi-Die Interconnect Bridge)やTSMCのCoWoS(Chip on Wafer-on-Substrate) 技術などのパッケージングオプションをサポートする予定だ。

ブレナン氏は、「将来的には、プロトコル層にも気を配らなければなりません」と語った。

CXL(Compute Express Link)プロトコルは、PCIe 5.0上に構築され、CPUチップパッケージとアクセラレータ、ストレージ、メモリコンポーネントを接続する業界標準として、当初はサポートされている。将来的には、ARM社が支援するAMBA(Advanced Microcontroller Bus Architecture)の一部であるCHI(Coherent Hub Interface)など、他の多くのプロトコルもサポートされる可能性がある。目標は、独自のプロトコルにマップアウトする機能を追加することと、企業がソフトウェアへの投資を保護できるようにプロトコルの後方互換性を持たせることである。

「また、将来的には、コンソーシアムのパートナーとともに、さまざまなフォームファクタ、管理、セキュリティ、その他多くのことを仕様化していく予定です」と、ブレナン氏は述べた。

ブレナン氏は、オンチップのUCIe設計の例をいくつか紹介した。1つは、CPUサブシステムとハードウェアアクセラレータ、管理およびセキュリティブロックをUCIeで接続したチップパッケージで、EMIBパッケージを使ってチップと分割DDR5メモリ、PCIeリンクに接続する。